# cādence°

**VIP Datasheet**

# Accelerated VIP for MIPI DSI

### Overview

Sometimes chips are just too big to verify with logic simulation software. SoCs comprised of tens of millions of logic gates will bog down software simulators, even when running on the fastest servers.

Simulating big designs requires hardware-assisted verification, an approach that uses special-purpose hardware, like Cadence® Palladium® XP systems, to dramatically boost simulation performance.

Cadence Accelerated VIPs are complementary products to Cadence simulation VIP and SpeedBridges. Accelerated VIPs are used to funnel data to the user's design-under-test and respond to stimulus received from it. Monitor functions such as collecting coverage and setting callbacks are not included.

Tuned for performance, AVIPs are an integral component in a simulation acceleration environment, speeding up verification 10's to 1,000's of times relative to simulation. The level of acceleration gain is dependent on the user's individual testbench and DUT synchronizations.

### **Specification Support**

The DSI AVIP is based on the following specifications:

- DSI BFM Requirement Specification, Version 0.5 22 May 2012

- MIPI Alliance Specification for Display Serial Interface (DSI), Version 1.1 - 22 November 2011

## **Usage Options**

| $\checkmark$            | Simulation Acceleration |

|-------------------------|-------------------------|

| $\overline{\checkmark}$ | HW/SW Co-Verification   |

# Supported Design-Under-Test Configurations

| $\checkmark$ | Master     | $\checkmark$ | Slave           | Hub/Switch |

|--------------|------------|--------------|-----------------|------------|

| $\checkmark$ | Full Stack |              | Controller-only | PHY-only   |

# **Product Highlights**

- Multi virtual-channel support in peripheral mode

- Fully configurable DSI packets in host mode

- Embedded digital model of D-PHY

- Configurable to DSI host or DSI peripheral

- Additional RGB 8:8:8 interface that can be connected directly to display module

- Bus turnaround support in both host and peripheral mode

- Error injection in host mode and error detection in peripheral mode supporting both DSI level (ECC, CRC) and low-level protocol error detection

HW/SW co-verification mode supports:

- Descriptor-based programming model

- Scalable internal memory for program and local data

- AHB slave interface providing full register access and internal memory access

- DMA and DMA scatter-gather capabilities via AHB master interface

- Incremental and pseudo-random data generation

- Configurable hardware and software start/stop conditions

- Support for simple and embedded programming loops

#### **Simulation Acceleration**

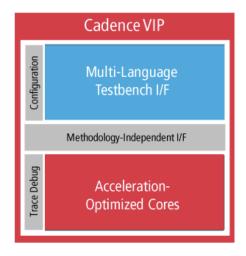

In simulation acceleration, the Cadence Palladium XP system works in conjunction with the Cadence Incisive® Simulator to divide up the simulation task. The Palladium XP runs the design under test while the Incisive simulator runs the testbench. Accelerated VIP is inserted for each of the standard interfaces in the design with the testbench interface running on Incisive and the acceleration-optimized core running on the Palladium XP.

Most of the testbench components employed in simulation can be reused, which saves set-up time and preserves the controllability and observeability of traditional logic simulation. With this approach, performance is often up to 1000X faster than logic simulation.

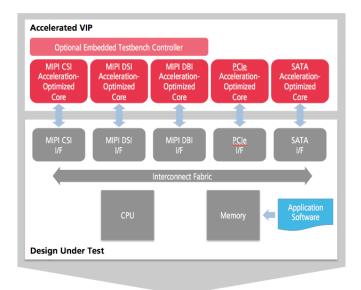

### **HW/SW Co-Verification**

With the HW/SW co-verification approach, both the test environment and the design under test run in the Palladium XP system. This results in huge performance gains – typically 10,000X to 100,000X faster than logic simulation. That kind of speed enables the verification of software along with the hardware design. This enables hardware/software integration bugs to be efficiently discovered and fixed – a task that would be nearly impossible to manage otherwise. To facilitate the HW/SW co-verification approach, application software is often used to run tests and monitor results.

Cadence Design Systems enables global electronic design innovation and plays an essential role in the creation of today's electronics. Customers use Cadence software, hardware, IP, and expertise to design and verify today's mobile, cloud, and connectivity applications. www.cadence.com